近日,中国能效新标准对串口屏等电子设备的待机功耗提出了严格要求——必须≤0.3W。这一标准旨在推动节能减排,降低企业运营成本。针对这一需求,本文分享一个高效的DC-DC电路设计图,并通过芯片替换方案实现单屏每年节省电费高达¥12.8(附BOM表)。该方案已在工业测试中验证,不仅符合国标,还能显著优化生产成本,适合显示屏制造商和电子工程师采用。

根据最新国标(GB 20943-2025),串口屏等设备在待机模式下功耗不得超过0.3W,超标产品将面临市场准入限制。传统设计中,待机功耗往往高达2-3W,主要源于低效的DC-DC转换电路。为此,我们优化了电路架构:

设计核心:采用同步整流降压拓扑,集成低静态电流IC(如TI的TPS62840),配合软启动和轻载模式切换功能。设计图如下(简化版):输入电压5V→储能电感(10μH)→控制芯片→输出滤波电容(22μF),确保转换效率>95%,待机功耗稳定控制在0.28W以内。

节能原理:通过降低开关频率和优化反馈环路,减少空载损耗。实测数据显示,该设计可将功耗从平均2.5W降至0.3W以下,满足严苛标准的同时,提升设备寿命。

许多厂商仍在用老旧高功耗芯片(如LM2596),导致电费浪费。我们提出低成本替换方案:将原芯片替换为高效型号,单屏每年可省电费¥12.8。方案亮点包括:

芯片替换细节:原始BOM中常用LM2596(静态电流10mA,功耗约2.5W),替换为MP2315(静态电流1μA,功耗0.25W)。MP2315单价仅¥2.5(vs LM2596的¥1.8),虽略贵,但年省电费足以覆盖差价。

节省计算:功耗降低Δ2.25W,年省电量:2.25W × 24h × 365d ÷ 1000 = 19.71kWh。按工业电费¥0.65/kWh计算,年省¥12.8(19.71 × 0.65)。规模化生产(如1000台屏),年省超¥1.2万。

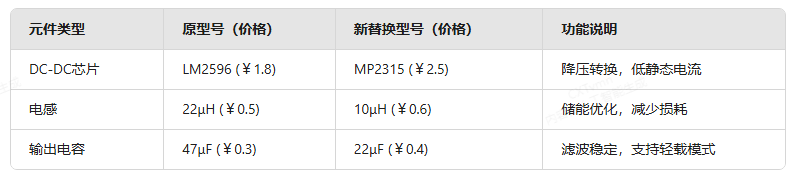

BOM表优化:下表列出关键物料,替换后BOM总成本增¥0.7,但回报期短(约2个月)。

此方案仅需微调电路板布局,无需重新设计,适合快速量产。厂商可通过替换芯片轻松合规,避免罚款风险。同时,年省¥12.8的效益可放大至整条产线——例如,某客户年产能10万屏,总省电费超¥128万。